FEUP FACULDADE DE ENGENHA

UNIVERSIDADE DO PORTO

# The shifting paradigm of teaching and learning

José Manuel Martins Ferreira | jmf@fe.up.pt | 26.01.2023

(online at https://bit.ly/26-01-2023)

### Roadmap

- 1. Forces of change (power balance)

- 2. Personal experience

- 3. Conclusion

# Forces of change (power balance)

Cinema

Sort by Date Y

we are waching all your videos at the cinema today. Having discussions....

@gmail.com

Re: Student survey

Is it ok if you get them on Thursday? We worked from home and I don't h ...

CCW3: Group 1 video

Hi, We ran into some problem with our video recording today, unfortun...

@gmail.com

Re: Student survey

I will do it tomorrow at school. Have a nice day! :) Sent from my iPhone

Video Presentation

Hello. Here comes the link to our last coursework video! BoundaryScanIn...

CCW3 video length

The video ended up being 13+ minutes long. Is this okay since the...

@gmail.com

Re: Student survey

They are filled out, just waiting to meet Alex this week. Sent from my i...

Jose Manuel Martins Ferreira

DFDS-3101: Deliverables deadli...

Dear Class, Just a reminder that you're expected to submit your deli...

To: Jose Ferreira Cinema

Inbox - HBV

às 08:31

Video

we are waching all your videos at the cinema today. Having discussions. All the other rooms on campus are in use for exams.

Best regards

## **Education hashtag in Tiktok**

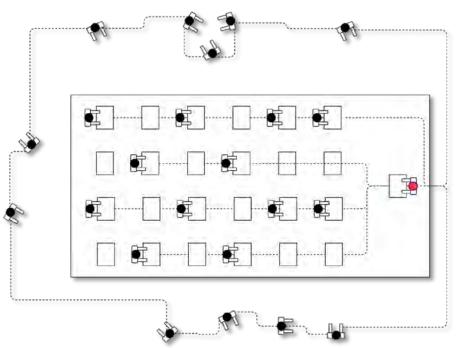

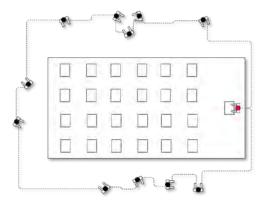

### "Tear down this wall!" (classroom)

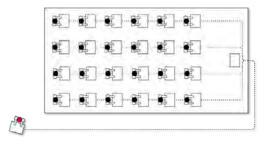

#### "Tear down this wall!" (lab)

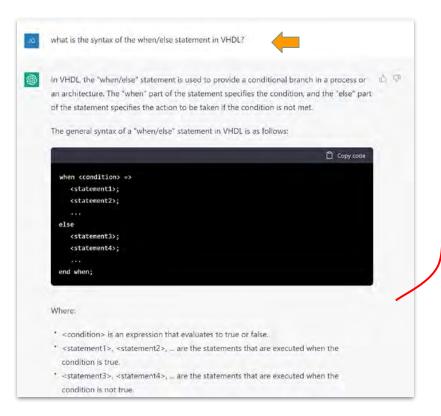

Do you know what is a sensitivity list in VHDL? G 17 In VHDL, a sensitivity list is a list of signals that a process is sensitive to. A process is a concurrent statement that describes the behavior of a digital system. It is executed in parallel with other processes. A process waits for changes on the signals in its sensitivity list, and when a change occurs on one of the signals, the process is activated and its statements are executed. The sensitivity list is specified in the "wait on" clause of the process statement. For example, if a process is sensitive to changes on signals A and B, the sensitivity list would be specified as: Copy code process(A, B) begin process statements end process; The process will be activated every time there's a change on either A or B. If the sensitivity

list is omitted, the process will not be activated by any signal, so it will have to wait for an

explicit "wait" statement.

```

The "when/else" statement can be used inside a process or an architecture, and it can be

nested within other "when/else" statements.

It's important to note that only one branch of a when/else statement will be executed based

on the condition.

Here's an example of a when/else statement in VHDL:

Copy code

process(clk)

if rising_edge(clk) then

if reset = '1' then

count <= (others => '0');

when count < max count =>

count <= count + 1;

count <= (others => '0');

end when:

end if;

end if:

end process;

In this example the process is sensitive to the clock edge, if the edge is rising and the reset

signal is '1' then the count variable is set to zero, otherwise, if the count is less than

max count, it will increase by 1, otherwise, it will be set to zero.

```

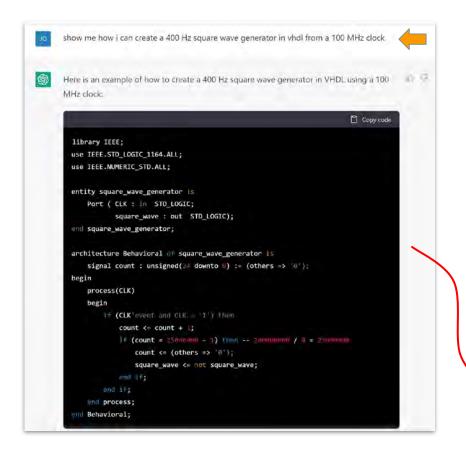

This VHDL code uses a 100 MHz clock as an input and generates a 400 Hz square wave as an output. The square wave frequency is determined by the value assigned to the "count" signal in the "if (count = 25000000 - 1)" statement. In this case, 25000000 is calculated by dividing the clock frequency (100 MHz) by the desired frequency of the square wave (400 Hz) times 2 (for a square wave). The output square\_wave is toggled everytime the count reaches the value of 25000000-1.

# Personal experience

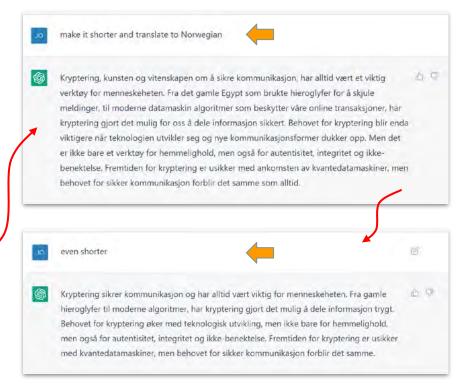

#### The course facilitator role

| TSD3070: Digital Circuit Synthesis (2022/23) |                                                                         |                                                                                                                          |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WEEK 0 (Prior reading)                       |                                                                         | Main topic & complementary information                                                                                   | Canvas content                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| (self-study)                                 |                                                                         | Setup and acquaintance - Basys-3 master constraints file  Main topic & complementary information                         | VIDEO: Welcome to this course! TOOL & LAB: Installation of Xilinx Vivade VIDEOS & LAB: Lab setup and acquaintance DISCUSSION: Concurrent nature of VHDL  Canvas content                                   | Lectures (7 lectures per day from 9 am to 4:15 pm)                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                              |                                                                         |                                                                                                                          |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

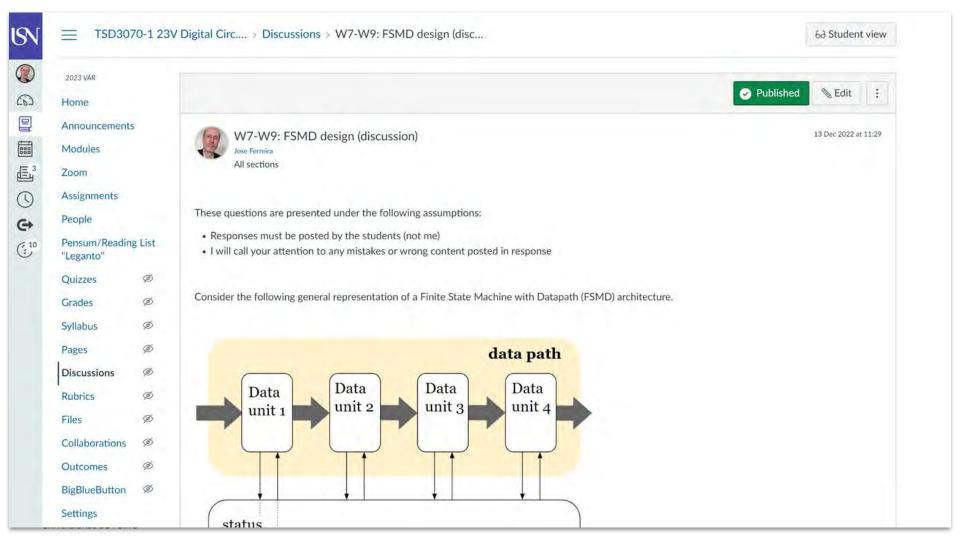

| Tuesday 10.01                                | (K_2229)<br>09:00-09:45<br>11:00-11:45<br>12:30-13:15<br>15:30-16:15    | The IEEE 1149.1 BST embedded test logic - course folder <u>link</u>                                                      | VIDEOS: Introduction to the BST std  LAB: Operation of the embedded test logict  DISCUSSION: The test cells  DISCUSSION: The BS instruction register  DISCUSSION: Timing issues: Delay between TAP states | Introduction to BST (why, overview of test logic and fault detection)     The BS cell (operation and VHDL description), the embedded test logic     Ira and BP cells (operation and VHDL descriptions), the BST instructions     The TAP controller: operation and VHDL description     Trainer 1149.1: Hands-on BS chain operation     Putting it all logether, SNT4BCT8244 data sheet revisited     Timing issues discussion, plan for tomorrow         |

| Wednesday 11.0                               | 01 (K_2229)<br>09:00-09:45<br>11:00-11:45<br>12:30-13:15<br>15:30-16:15 | BST board testing - notes folder <u>link</u>                                                                             | VIDEOS: Fault detection with BST DISCUSSION: SN74BCT8244: Output pin control DISCUSSION: SN74BCT8244. Output behaviour DISCUSSION: Open fault inside a cluster                                            | Recap of yesterday     Board testing (BS chain, shorts and opens)     Board test short-circuit among pins in different chains (X9)     Board test: open-circuit fault inside cluster (X1)     Board test: short-circuit fault inside cluster (X2)     Board test: infrastructure fault (X16)     SN74BCT8244 PRPG and SA modes, plan for tomorrow                                                                                                         |

| Thursday 12.01                               | (K_2229)<br>09:00-09:45<br>11:00-11:45<br>12:30-13:15<br>15:30-16:15    | Finite State Machines with Datapath (introduction)  - code folder link  - templates for top level and an RS232 testbench | VIDEOS & LAB: Finite state machines with datapath LAB: Receive ASCII via RS232 and display on Basys-3                                                                                                     | Introduction to FSMDs (what, ASMD representation rules)     Multiply by adding: FSMD architecture and operation     Multiply by adding: ASMD chart     Multiply by adding: Vivado project     Multiply by adding: Vivado project     Multiply by adding: Vivado project     Multiply by adding: single file implementation     Multiply by adding: single file implementation     Tolsplay ASCII codes received via RS232 (lab script), plan for tomorrow |

| Friday 13.01                                 | (K_2229)<br>09:00-09:45<br>11:00-11:45<br>12:30-13:15<br>15:30-16:15    | Finite State Machines with Datapath (practice)  - code folder <u>link</u> jmf@fe.up.p                                    | VIDEO & LAB: Napoleon's cipher DISCUSSION: Napoleon's cipher handling backspaces at   https://bit.ly/26-01-2023                                                                                           | Introduction to Napoleon's cipher (operation)     Napoleon's cipher: FSMD architecture     Napoleon's cipher: ASMD chart     Napoleon's cipher: Vivado project     Napoleon's cipher: Vivado project     Napoleon's cipher: Vivado project     Introduction to the first coursework assignment (with demo)     Wrap-up and plan for the following weeks                                                                                                   |

# \*Tear down 12/02 whis wall!" (classroom)

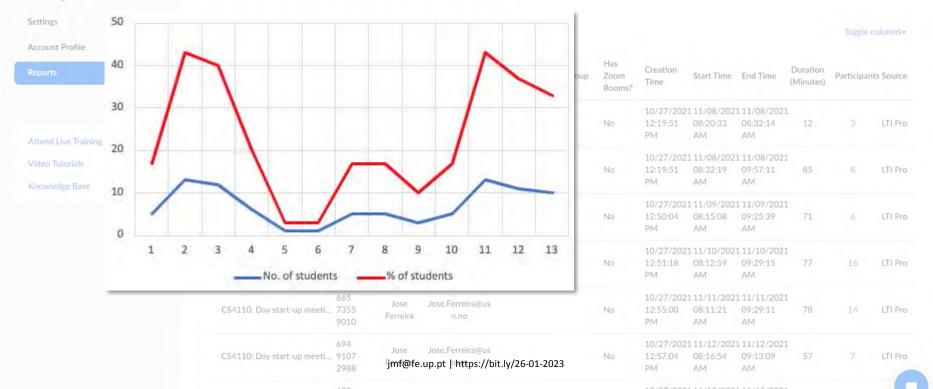

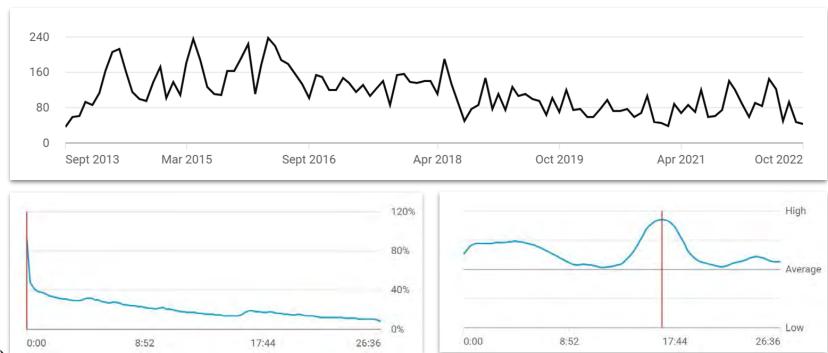

Webinars Maximum report duration: 1 Month

Recordings

Reports show information for meetings that ended at least 15 minutes ago.

#### "Tear down this wall!" (classroom)

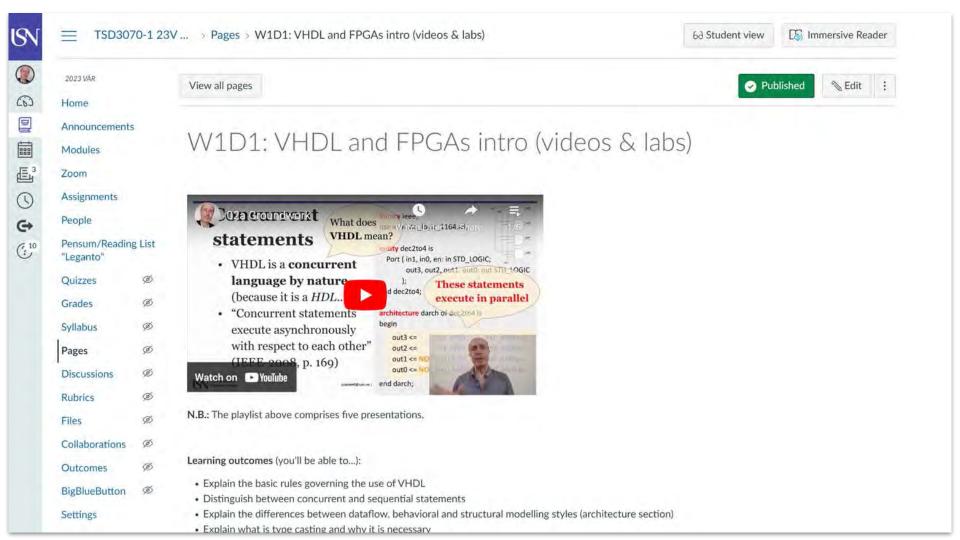

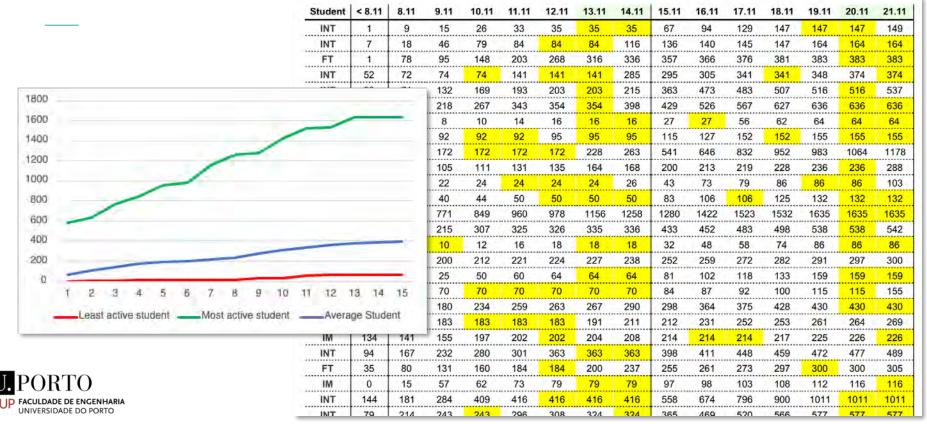

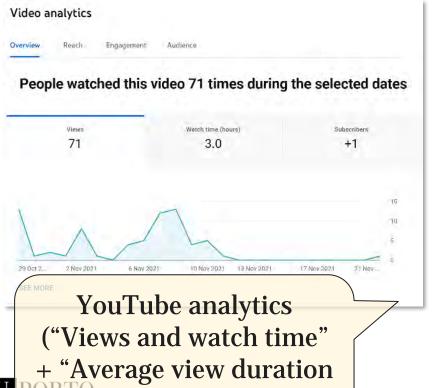

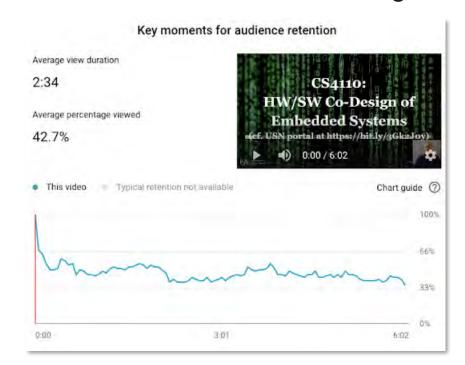

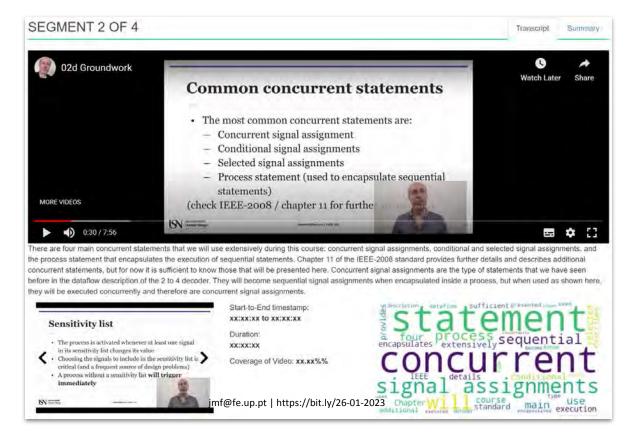

Video content for course delivery

uldale bepercentage viewed")

# Video content and hybrid delivery

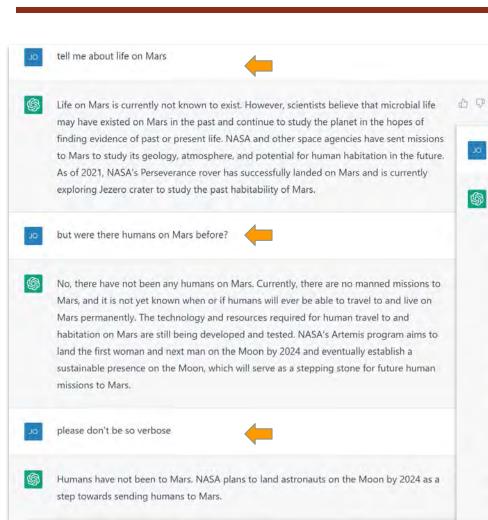

## ChatGPT as a teaching assistant

#### **VHDL** and ChatGPT

- ChatGPT is a great source of help to clarify doubts

- Possibly the most important aspect (as in many other situations in life...) is to know what questions to ask

- Create an account at https://chat.openai.com/ and avoid peak times

Recommenda tion to students

semmf@usn.no ( TSD3070

61

# Conclusion

### Challenges vs. opportunities

- "Course facilitator" profile:

- Provide organization and context (what, when, who, how)

- Adapt existing materials to new T&L contexts (e.g., transform slide sets into short video presentations)

- Integrate new tools as they emerge (e.g., ChatGPT)

- Always innovate (what comes next?)

### Learn from bad/poor videos

#### Video transformation

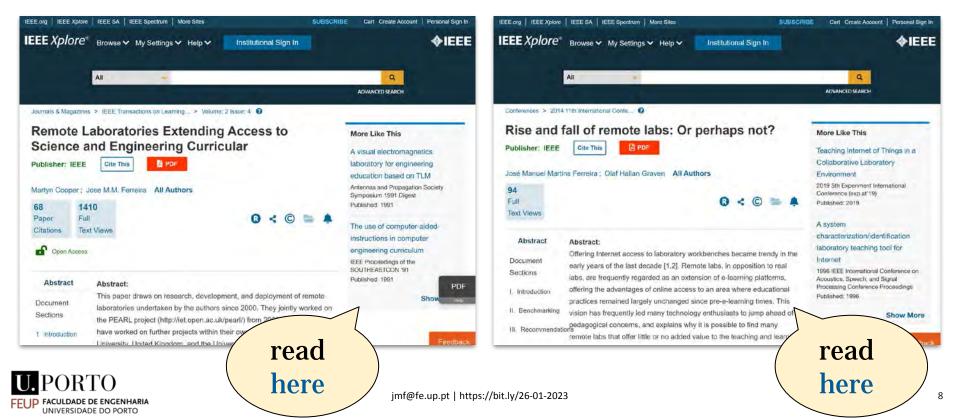

#### (R) labs for formative assessment

View metadata, citation and similar papers at core.ac.uk

brought to you by CORE

provided by Repositorio Aberto dia Universidade do Porto

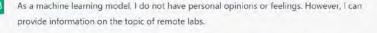

Embedding formative assessment features into LabView interfaces

#### Embedding formative assessment features into LabView interfaces

Max Conradi<sup>1</sup>, Reinhard Langmann<sup>1</sup>, António M. Cardoso<sup>2</sup>, J. M. Ferreira<sup>2</sup>

<sup>1</sup> University of Applied Sciences, Dusseldorf, Germany

<sup>2</sup> Faculdade de Engenharia, Universidade do Porto, Portugal

read here

Abstract— Virtual instruments (VI), namely those designed using LabView, are increasingly used to enable access to remote instruments over the web. In an academic context, such VIs may be used to build a remote workbench that enables the students to carry out a laboratory task from their homes. Remote workbenches, or simulation environments, are not meant to replace real labs, but rather to complement them. They enable the students to continue their work in the lab, even after leaving the university campus. In most cases, a remote workbench constitutes a replica of what the student sees in a real workbench. However, VI interfaces may be designed to provide a much richer educational experience, namely by embedding formative assessment features, as described in this work-in-progress paper.

Index Terms— e-learning, formative assessment, online labs, LabView. jmf@fe.up.pt | https://bit.ly/26-01-2023

The students running an experiment will have to adjust the waveform generator and the oscilloscope. If this was done in a real lab, with a tutor nearby, he/she would be able to assess if the student knew how to handle these instruments, just by watching how the student carried out this first step. The objective of this work is to study how far the same conclusion can be derived by automatically monitoring how the student handles the VIs.

#### II. REFERENCE MODEL

The PTSE lab at FEUP already uses various VIs that are used to design remote experiments in electronics. All such VIs were developed using LabView. The proposed approach consists of analysing the LabView scripts for such VIs and devising ways to identify and capture the relevant embedded assessment information. In the initial phase of this work, a simple VI representing a basic instrument (e.g. a voltmeter) was used to look for an

# Let ChatGPT have a say:)

Remote labs, also known as virtual labs or online labs, are laboratory environments that are accessed remotely, typically through the internet. They allow students and researchers to access laboratory equipment, simulations, and other resources from anywhere, at any time.

Remote labs have a number of advantages over traditional, physical labs. They can provide access to equipment and resources that might not be available locally, and they can also allow for more flexible scheduling and greater collaboration among students and researchers. Additionally, remote labs can also be used to increase the number of students that can access equipment and resources, and they can also be used to provide access to labs for remote students or students in different locations.

However, remote labs also have some limitations. They may not be able to replicate all of the features and capabilities of physical labs, and they may also require specialized equipment or software to access. Additionally, they also might require internet access and a reliable connection, which can be an issue in some locations.

Overall, remote labs can be a valuable tool for students and researchers to access laboratory equipment and resources, but the limitations should be taken into account when planning and using them.

will remote labs replace real labs?

It is unlikely that remote labs will completely replace traditional, physical labs. While remote the substance of advantages, such as greater flexibility and accessibility, they also have limitations that may make them less suitable for certain types of experimentation or research.

Moreover, some experiments and research require the use of hazardous or toxic materials that are not suitable to be used in a remote environment and can only be used in physical labs.

However, remote labs can be a valuable supplement to traditional, physical labs, by allowing students and researchers to access equipment and resources that might not be available locally, and by providing a more flexible and collaborative environment for experimentation and research. Remote labs can also be useful for providing additional access to labs for remote students or students in different locations, or increasing the number of students that can access equipment and resources.

In conclusion, remote labs can be a powerful tool for conducting research and experiments, but it's unlikely that they will completely replace traditional physical labs, as both have their unique advantages and disadvantages that make them suitable for different types of research and experiments.

Let you have a say now!:)

José Manuel Martins Ferreira | jmf@fe.up.pt | 26.01.2023

(online at https://bit.ly/26-01-2023)